Data sheet acquired from Harris Semiconductor

SCHS188

CD74HC534, CD74HCT534,

CD74HC564, CD74HCT564

High Speed CMOS Logic Octal D-Type Flip-Flop,

Three-State Inverting Positive-Edge Triggered

Description

The Harris CD74HC534, CD74HCT534, CD74HC564 and

CD74HCT564 are high speed Octal D-Type Flip-Flops manu-

factured with silicon gate CMOS technology. They possess

the low power consumption of standard CMOS integrated cir-

cuits, as well as the ability to drive 15 LSTTL loads. Due to the

large output drive capability and the three-state feature, these

devices are ideally suited for interfacing with bus lines in a bus

organized system. The two types are functionally identical and

differ only in their pinout arrangements.

The CD74HC534, CD74HCT534, CD74HC564 and

CD74HCT564 are positive edge triggered flip-flops. Data at

the D inputs, meeting the setup and hold time requirements,

are inverted and transferred to the Q outputs on the positive

going transition of the CLOCK input. When a high logic level is

applied to the OUTPUT ENABLE input, all outputs go to a

high impedance state, regardless of what signals are present

at the other inputs and the state of the storage elements.

The CD74HCT logic family is speed, function, and pin

compatible with the standard 74LS logic family.

January 1998

Features

鈥?Buffered Inputs

[ /Title

(CD74

HC534

,

CD74

HCT53

4,

CD74

HC564

,

CD74

HCT56

鈥?Common Three-State Output-Enable Control

鈥?Three-State Outputs

鈥?Bus Line Driving Capability

鈥?Typical Propagation Delay = 13ns at V

CC

= 5V,

C

L

= 15pF, T

A

= 25

o

C (Clock to Output)

鈥?Fanout (Over Temperature Range)

- Standard Outputs . . . . . . . . . . . . . . . 10 LSTTL Loads

- Bus Driver Outputs . . . . . . . . . . . . . 15 LSTTL Loads

鈥?Wide Operating Temperature Range . . . -55

o

C to 125

o

C

鈥?Balanced Propagation Delay and Transition Times

鈥?Signi鏗乧ant Power Reduction Compared to LSTTL

Logic ICs

鈥?HC Types

- 2V to 6V Operation

- High Noise Immunity: N

IL

= 30%, N

IH

= 30% of V

CC

at V

CC

= 5V

鈥?HCT Types

- 4.5V to 5.5V Operation

- Direct LSTTL Input Logic Compatibility,

V

IL

= 0.8V (Max), V

IH

= 2V (Min)

- CMOS Input Compatibility, I

l

鈮?/div>

1碌A(chǔ) at V

OL

, V

OH

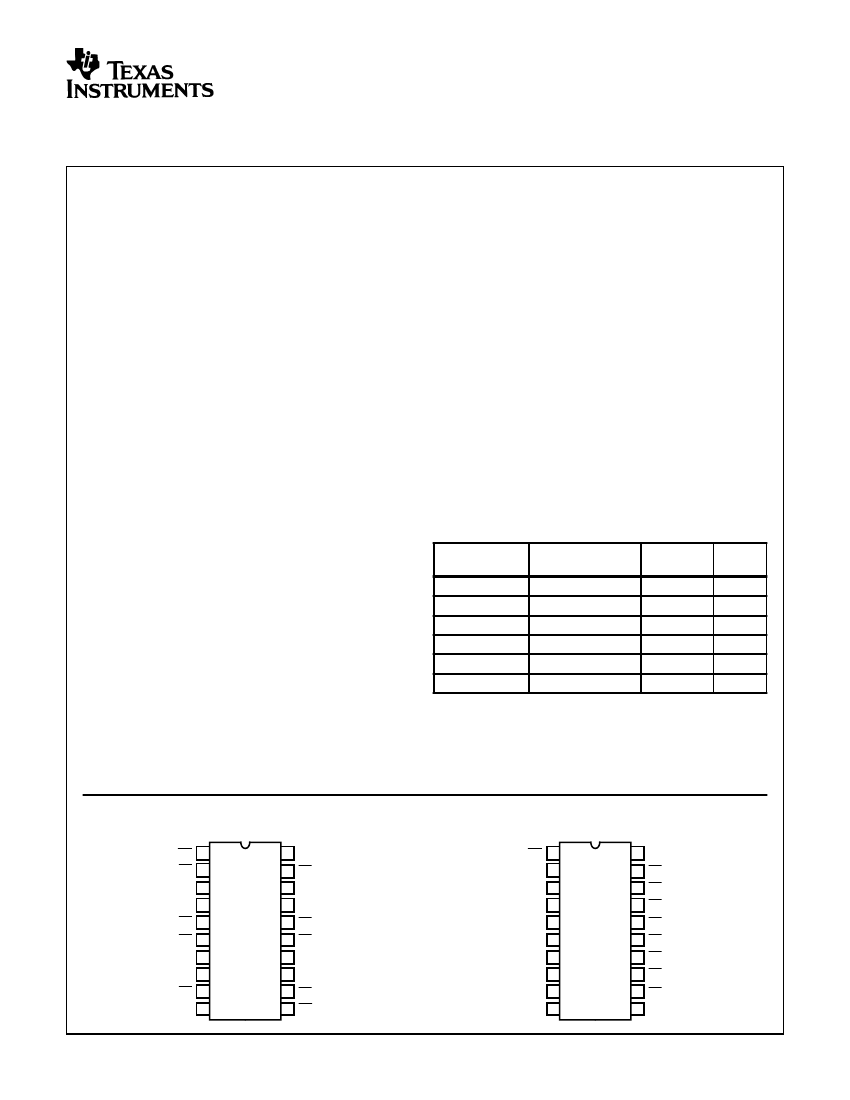

Ordering Information

PART NUMBER

CD74HC534E

CD74HCT534E

CD74HC564E

CD74HCT564E

CD74HC564M

CD74HCT564M

TEMP. RANGE (

o

C)

-55 to 125

-55 to 125

-55 to 125

-55 to 125

-55 to 125

-55 to 125

PACKAGE

20 Ld PDIP

20 Ld PDIP

20 Ld PDIP

20 Ld PDIP

20 Ld SOIC

20 Ld SOIC

PKG.

NO.

E20.3

E20.3

E20.3

E20.3

M20.3

M20.3

NOTES:

1. When ordering, use the entire part number. Add the suf鏗亁 96 to

obtain the variant in the tape and reel.

2. Wafer and die for this part number is available which meets all

electrical specifications. Please contact your local sales office or

Harris customer service for ordering information.

Pinouts

CD74HC534, CD74HCT534

TOP VIEW

OE

Q0

D0

D1

Q1

Q2

D2

D3

Q3

1

2

3

4

5

6

7

8

9

(PDIP)

CD74HC564, CD74HCT564

TOP VIEW

OE

D0

D1

D2

D3

D4

D5

D6

D7

1

2

3

4

5

6

7

8

9

(PDIP, SOIC)

20 V

CC

19 Q0

18 Q1

17 Q2

16 Q3

15 Q4

14 Q5

13 Q6

12 Q7

11 CP

20 V

CC

19 Q7

18 D7

17 D6

16 Q6

15 Q5

14 D5

13 D4

12 Q4

11 CP

GND 10

GND 10

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright

漏

Harris Corporation 1998

File Number

1640.1

1