Fact Sheet

MPC7450/MPC7451

HIGH PERFORMANCE

HOST MICROPROCESSOR

The MPC7450/MPC7451 host processor is a high-

performance, low-power, 32-bit implementation of the

PowerPC RISC architecture with a full 128-bit

implementation of Motorola鈥檚 AltiVec鈩?technology. This

microprocessor is ideal for leading-edge computing, em-

bedded network control, and signal processing

applications. The MPC7450/MPC7451 has a deep, seven-

stage pipeline with 11 execution units. The L2 cache has

been integrated onto the die for greater speed, and

supports a large backside L3 cache with a 64-bit

datapath. The MPC7450/MPC7451 offers increased

address space and high-bandwidth MPX bus with

minimized signal setup times and reduced idle cycles to

increase bus bandwidth to a maximum speed of 133 MHz.

MPC7450/MPC7451 processors offer single-cycle,

throughput, double-precision, floating-point performance

and full symmetric multi-processing (SMP) capabilities.

Finally, the MPC7450/MPC7451 is software-compatible

with existing MPC6xx, MPC7xx, and MPC74xx host

processors and exploits the full potential of AltiVec

technology.

SUPERSCALAR MICROPROCESSOR

MPC7450/MPC7451 microprocessors feature a high-frequency superscalar G4 core,

capable of issuing four instructions per clock cycle (three instructions + branch) into 11

independent execution units:

鈥?Four integer units (3 simple + 1 complex)

鈥?Double-precision floating-point unit

鈥?Four AltiVec units (simple, complex, floating, and permute)

鈥?Load/store unit

鈥?Branch processing unit

CACHE AND MMU SUPPORT

The MPC7450/MPC7451 microprocessor has separate 32 KB, physically addressed

instruction and data caches. Both L1 caches feature cache way locking and are eight-way

set associative. For greater speed, the L2 cache has been integrated on-chip with a 256-

bit interface to L1 which operates at processor frequency. This L2 is 256 kB eight-way set

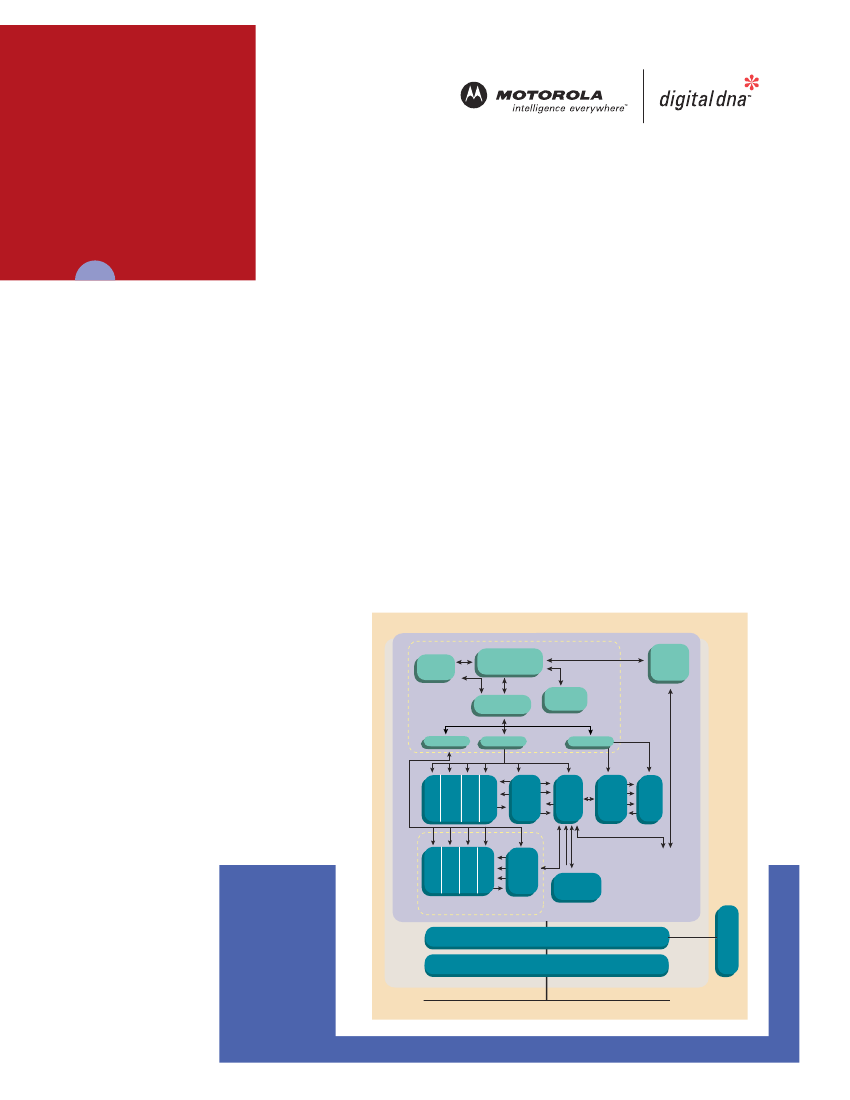

MPC7450/MPC7451 BLOCK DIAGRAM

Completion

Unit

Instruction Fetch

Branch Unit

Sequencer Unit

32 KB

Instruction

Cache

Dispatch Unit

BHT/

BTIC

AltiVec Issue

GPR Issue

FPR Issue

CFX SFXO SFX1 SFX2

GPRs

Rename

Buffers

LSU

FPRs

Rename

Buffers

FPU

VRs

Rename

Buffers

32 kB

Data

Cache

Interface

to Memory

Sub-System

COMPLEX

PERMUTE

SIMPLE

Unified L2 Cache/Tag L3 Control

System Interface Unit

60x/MPX bus interface

L3 Cache

FLOAT

AltiVec Engine