SDC-630/632/634* A/ST

10-, 12-, OR 14-BIT SYNCHRO-TO-DIGITAL/

RESOLVER-TO-DIGITAL CONVERTER

LOWER COST! PIN-FOR-PIN REPLACEMENT FOR

SDC-630/632/634 SERIES.

FOR ALL NEW DESIGNS!

FEATURES

DESCRIPTION

The SDC-630/632/634 A/ST series

are low cost, low profile synchro-to-

digital (S/D) and resolver-to-digital

(R/D) tracking converters with stan-

dard pin configurations. They use a

unique control transformer algorithm

that provides inherently higher accu-

racy and jitter-free output. Utilizing a

type II servo loop, these converters

have no velocity lag up to the speci-

fied tracking rate, and output data is

always fresh and continuously avail-

able. Each unit is fully trimmed and

requires no adjustment or field cali-

bration.

APPLICATIONS

These converters may be used wher-

ever analog angle data from a syn-

chro or resolver must be rapidly and

accurately converted to digital form

for transmission, storage or analysis.

Because these units are extremely

rugged and stable, and meet the

requirements on MIL-STD-202E, they

are suitable for the most severe

industrial, commercial and military

applications. Military ground support

and avionics uses include ordnance

control, radar tracking systems, navi-

gation and collision avoidance sys-

tems.

鈥?/div>

Low Cost Pin-for-Pin

Replacement

for SDC-630/632/634 Series

鈥?/div>

Industry Standard Low Profile

Modular Converters

鈥?/div>

Accuracy:

10 Bit: 21 Minutes

12 Bit: 8.5 Minutes

14 Bit: 4 Minutes, 0.9 LSB or

2.6 Minutes (High Accuracy)

鈥?/div>

Options (Consult Factory):

Velocity Input

BIT: Built-In-Test

16-Bit Resolution

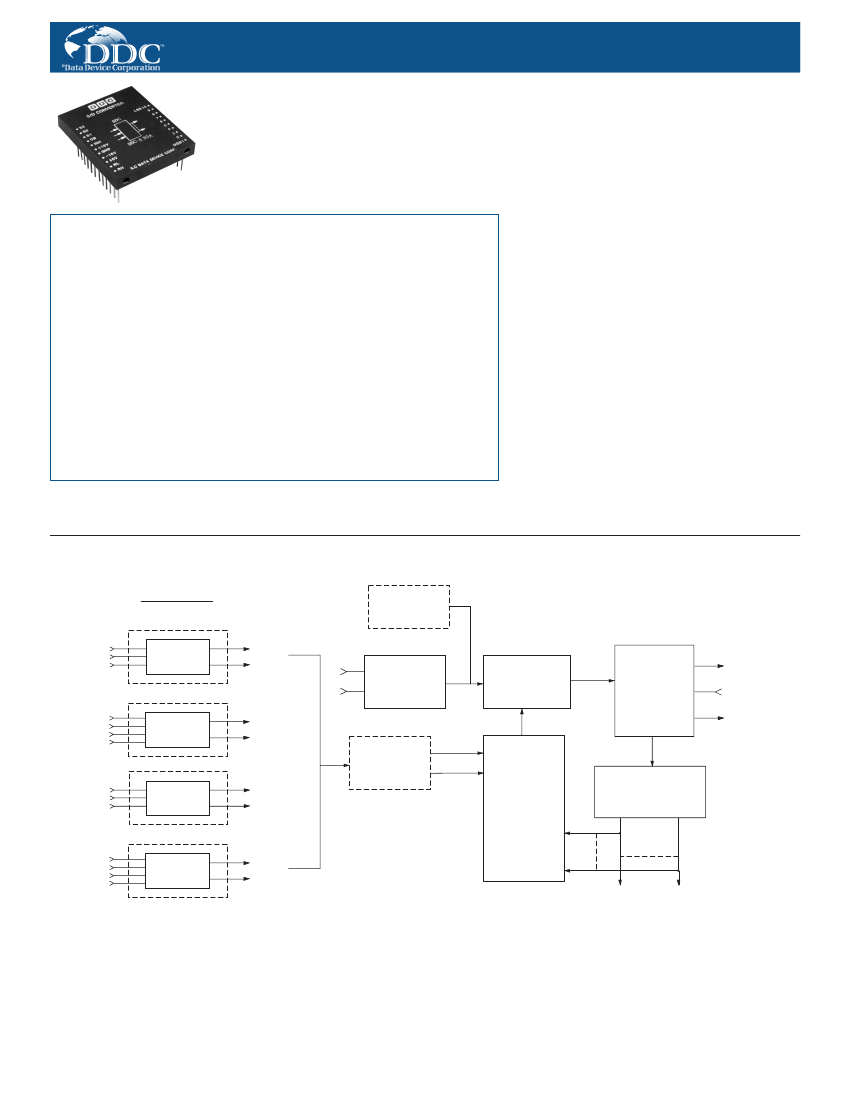

INPUT OPTIONS

SYNCHRO INPUT OPTION (A)

RESISTOR (ST)

DIVIDER

S1

S2

S3

SCOTT-T

TRANSFORMER

SIN

胃

COS

胃

RH

RL

RESOLVER INPUT OPTION (A)

S1

S2

S3

S4

REFERENCE (A)

ISOLATION

TRANSFORMER

REF

DEMODULATOR

SIN

(胃 鈭?蠁)

RESOLVER

ISOLATION

TRANSFORMER

SIN

胃

COS

胃

SIN

胃

SIN

(胃 鈭?蠁)

COS

蠅

t

ERROR

PROCESSOR

AND

VOLTAGE

CONTROLLED

OSCILLATOR

VEL

VELOCITY

(OPTIONAL)

INH

INHIBIT

CB

CONVERTER

BUSY

SYNCHRO INPUT OPTION (ST)

INPUT

OPTION

SIN

胃

COS

胃

COS

胃

S1

S2

S3

SOLID STATE

SCOTT-T

BUFFER

SOLID STATE

CONTROL

TRANSFORMER

(CT)

UP-DOWN COUNTER

(CONTAINS ANGLE

蠁

)

RESOLVER INPUT OPTION (ST)

S1

S2

S3

S4

BIT 1

SIN

胃

COS

胃

BIT 10,

12 OR 14

SOLID STATE

RESOLVER

BUFFER

BIT 1

(MSB)

BIT 10, 12, OR 14

(LSB)

FIGURE 1. SDC-630/632/634 A/ST BLOCK DIAGRAM

* Patented

漏

1993, 1999 Data Device Corporation