M28256

256 Kbit (32Kb x8) Parallel EEPROM

with Software Data Protection

PRELIMINARY DATA

FAST ACCESS TIME:

鈥?90ns at 5V

鈥?120ns at 3V

SINGLE SUPPLY VOLTAGE:

鈥?5V

鹵

10% for M28256

鈥?2.7V to 3.6V for M28256-xxW

LOW POWER CONSUMPTION

FAST WRITE CYCLE:

鈥?64 Bytes Page Write Operation

鈥?Byte or Page Write Cycle

ENHANCED END of WRITE DETECTION:

鈥?Data Polling

鈥?Toggle Bit

STATUS REGISTER

HIGH RELIABILITY DOUBLE POLYSILICON,

CMOS TECHNOLOGY:

鈥?Endurance >100,000 Erase/Write Cycles

鈥?Data Retention >10 Years

JEDEC APPROVED BYTEWIDE PIN OUT

ADDRESS and DATA LATCHED ON-CHIP

SOFTWARE DATA PROTECTION

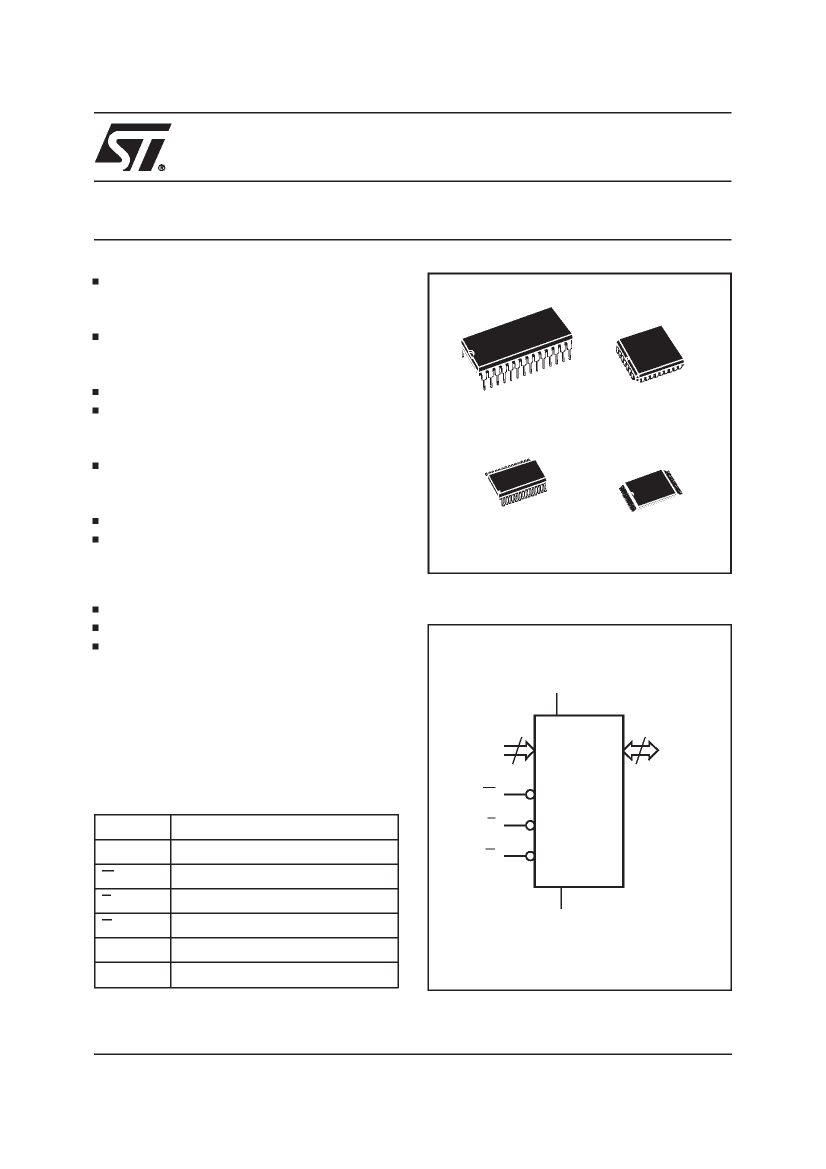

28

1

PDIP28 (BS)

PLCC32 (KA)

28

1

SO28 (MS)

300 mils

TSOP28 (NS)

8 x13.4mm

Figure 1. Logic Diagram

VCC

DESCRIPTION

The M28256 and M28256-Ware 32K x8 low power

Parallel EEPROM fabricatedwith STMicroelectron-

ics proprietary double polysilicon CMOS technol-

ogy.

Table 1. Signal Names

A0-A14

DQ0-DQ7

W

E

G

V

CC

V

SS

Address Input

Data Input / Output

Write Enable

Chip Enable

Output Enable

Supply Voltage

Ground

15

A0-A14

8

DQ0-DQ7

W

E

G

M28256

VSS

AI01885

January 1999

This is preliminary information on a new product now in developmentor undergoing evaluation . Detail s are subject to change without notice.

1/21

![]() STMICROELECTRONICS

STMICROELECTRONICS